## Abstraction Layer for Implementation of Extensions IN PROGRAMMABLE NETWORKS

Collaborative project co-funded by the European Commission within the Seventh Framework Programme

| Grant agreement no: | 317880                                                                        |

|---------------------|-------------------------------------------------------------------------------|

| Project acronym:    | ALIEN                                                                         |

| Project full title: | "Abstraction Layer for Implementation of Extensions in programmable Networks" |

| Project start date: | 01/10/12                                                                      |

| Project duration:   | 24 months                                                                     |

## Deliverable D3.1 Hardware platforms and switching constraints

Version 1.0

| Due date:           | 28/02/2013                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Submission date:    | 28/02/2013                                                                                                                                                                                                                                                                                                                                                                     |

| Deliverable leader: | UCL                                                                                                                                                                                                                                                                                                                                                                            |

| Author list:        | Richard G. Clegg, Raul Landa (UCL), Remigiusz Rajewski, Marek Michalski (PUT), Artur<br>Binczewski, Bartosz Belter, Damian Parniewicz, Iwo Olszewski, Łukasz Ogrodowczyk,<br>Krzysztof Dombek, Artur Juszczyk (PSNC), Matteo Gerola (Create-Net), Mehdi<br>Rashidfard (UBristol), Marc Bruyere (Dell/Force 10), Jon Matias (UPV/EHU), Hagen<br>Woesner, Andreas Koespel (EICT) |

#### **Dissemination Level**

| $\boxtimes$ | PU: | Public                                                                                |

|-------------|-----|---------------------------------------------------------------------------------------|

|             | PP: | Restricted to other programme participants (including the Commission Services)        |

|             | RE: | Restricted to a group specified by the consortium (including the Commission Services) |

|             | CO: | Confidential, only for members of the consortium (including the Commission Services)  |

© Authors and their corresponding institutions

License: CC-BY-NC http://creativecommons.org/licenses/by-nc/4.0/legalcode

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page.

#### Abstract

The main purpose of this document is to describe in detail the equipment (ALIEN hardware) at each partner site. This description is sufficiently detailed as to include the exposed protocols for data and control and the transmission mechanisms used by the hardware. The aim of the document is to present the information in such a way as to gather common themes which will be useful in the design of the Hardware Abstraction Layer (HAL).

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## Table of Contents

| Та  | ble of ( | Conten                  | ts                         | 3  |  |

|-----|----------|-------------------------|----------------------------|----|--|

| Fig | gure Su  | mmary                   | /                          | 7  |  |

| Та  | ble Sur  | nmary                   |                            | 9  |  |

| Ex  | ecutive  | e Summ                  | nary                       | 10 |  |

| 1   | Intro    | duction                 | 1                          | 11 |  |

| 2   | Testb    | eds                     |                            | 12 |  |

|     | 2.1      | PUT te                  | estbed                     | 12 |  |

|     | 2.2      | UCL te                  | estbed                     | 14 |  |

|     | 2.3      | PSNC testbed 15         |                            |    |  |

|     | 2.4      | UPV/EHU testbed 16      |                            |    |  |

|     | 2.5      | EICT testbed 17         |                            |    |  |

|     | 2.6      | 5 Bristol testbed 18    |                            |    |  |

|     | 2.7      | Dell/Force10 testbed 20 |                            |    |  |

|     | 2.8      | CREAT                   | FE-NET testbed             | 21 |  |

| 3   | EZapp    | oliance                 |                            | 23 |  |

|     | 3.1      | Overvi                  | iew                        | 23 |  |

|     |          | 3.1.1                   | Physical box overview      | 23 |  |

|     | 3.2      | Data p                  | blane                      | 25 |  |

|     |          | 3.2.1                   | Transmission technology    | 25 |  |

|     |          | 3.2.2                   | Switching management rules | 27 |  |

|     | 3.3      | Contro                  | ol/management plane        | 28 |  |

|     |          | 3.3.1                   | Plane purpose              | 28 |  |

|     |          | 3.3.2                   | Exposed protocols          | 29 |  |

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

|            |             |           |                                                    | ↓<br>•<br>•<br>• |

|------------|-------------|-----------|----------------------------------------------------|------------------|

| D3.1 Hardw | are platfoi | ms and sv | witching constraints<br>Configuration requirements | 29               |

| 4          | GEPO        | N         |                                                    | 30               |

|            | 4.1         | Overv     | iew                                                | 30               |

|            |             | 4.1.1     | Physical box overview                              | 30               |

|            | 4.2         | Data p    | blane                                              | 31               |

|            |             | 4.2.1     | Transmission technology                            | 31               |

|            |             | 4.2.2     | Switching management rules                         | 32               |

|            | 4.3         | Contro    | ol/management plane                                | 32               |

|            |             | 4.3.1     | Plane purpose                                      | 32               |

|            |             | 4.3.2     | Exposed protocols                                  | 33               |

|            |             | 4.3.3     | Configuration requirements                         | 34               |

| 5          | NetFF       | ΡĠΑ       |                                                    | 35               |

|            | 5.1         | The No    | etFPGA Card Overview                               | 35               |

|            |             | 5.1.1     | Physical Box Overview                              | 36               |

|            | 5.2         | Data P    | Plane                                              | 37               |

|            |             | 5.2.1     | Transmission technology                            | 37               |

|            |             | 5.2.2     | Switching Management Rules                         | 39               |

|            | 5.3         | Contro    | ol/Management Plane                                | 40               |

|            |             | 5.3.1     | Plane Purpose                                      | 40               |

|            |             | 5.3.2     | Exposed Protocols                                  | 41               |

|            |             | 5.3.3     | Configuration Requirements                         | 41               |

| 6          | DOCS        | IS        |                                                    | 42               |

|            | 6.1         | Physic    | cal box overview                                   | 43               |

|            | 6.2         | Data p    | blane                                              | 45               |

|            |             | 6.2.1     | Transmission technology                            | 45               |

|            |             | 6.2.2     | Switching management rules                         | 46               |

|            | 6.3         | Contro    | ol/management plane                                | 47               |

|            |             | 6.3.1     | Plane purpose                                      | 47               |

|            |             | 6.3.2     | Exposed protocols                                  | 48               |

|            |             | 6.3.3     | Configuration requirements                         | 48               |

| 7          | ATCA        | 49        |                                                    |                  |

|            | 7.1         | Overv     | iew                                                | 49               |

|     | 7.1.1  | Physical box overview | 49 |

|-----|--------|-----------------------|----|

| 7.2 | Data p | lane                  | 50 |

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

| ardware platf |           | vitching constraints                                    |    |

|---------------|-----------|---------------------------------------------------------|----|

|               | 7.2.1     | Transmission technology                                 | 50 |

|               | 7.2.2     | Switching management rules                              | 51 |

| 7.3           |           | ol/management plane                                     | 51 |

|               | 7.3.1     | Plane purpose                                           | 51 |

|               | 7.3.2     | Exposed protocols                                       | 52 |

|               | 7.3.3     | Configuration requirements                              | 52 |

| 8 Laye        | r 0 swite | ch                                                      | 53 |

| 8.1           | Overvi    | iew                                                     | 53 |

|               | 8.1.1     | Physical box overview                                   | 53 |

| 8.2           | Data p    | lane                                                    | 54 |

|               | 8.2.1     | Transmission technology                                 | 54 |

|               | 8.2.2     | Switching management rules                              | 59 |

| 8.3           | Contro    | ol/management plane                                     | 60 |

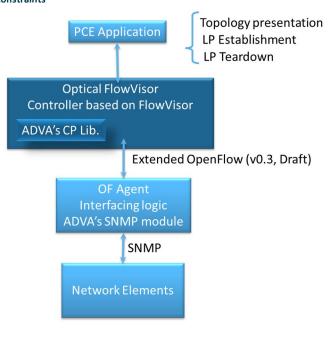

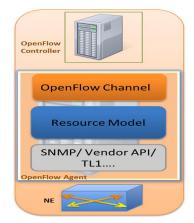

|               | 8.3.1     | Adaptation of ADVA's optical ROADM to OpenFlow protocol | 60 |

|               | 8.3.2     | Plane purpose                                           | 63 |

|               | 8.3.3     | Exposed protocols                                       | 64 |

|               | 8.3.4     | Configuration requirements                              | 64 |

| 9 Dell/       | Force10   | ) switch                                                | 65 |

| 9.1           | Overvi    | iew                                                     | 65 |

|               | 9.1.1     | Physical box overview                                   | 65 |

| 9.2           | Data p    | lane                                                    | 66 |

|               | 9.2.1     | Transmission technology                                 | 68 |

|               | 9.2.2     | Switching management rules                              | 68 |

| 9.3           | Contro    | bl/management plane                                     | 68 |

|               | 9.3.1     | Plane purpose                                           | 68 |

|               | 9.3.2     | Exposed protocols                                       | 68 |

|               | 9.3.3     | Configuration requirements                              | 69 |

| 10 Com        | mon ha    | rdware themes                                           | 70 |

| 10.1          | Packet    | t Processing Devices                                    | 70 |

| 10.2          | Lightp    | ath devices                                             | 71 |

| 10.3          | Point t   | to multi-point devices                                  | 72 |

| 10.4          |           | ammable network processors                              | 73 |

| 10.5          | -         | ally reconfigurable systems                             | 74 |

| 11 Conc       | lusions   | Future directions for HAL design                        | 75 |

| 50.10         |           |                                                         |    |

| D3.1 Hardware platforms and switching constraints |    |

|---------------------------------------------------|----|

| 12 References                                     | 76 |

| 13 Acronyms                                       | 77 |

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

+

# **Figure Summary**

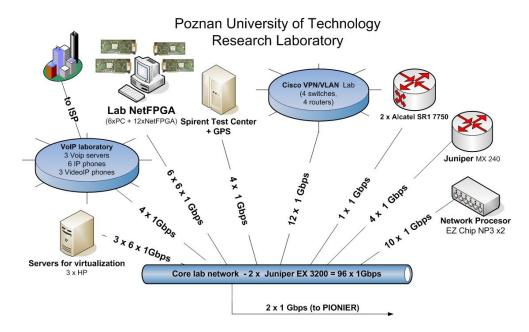

| Figure 2.1 PUT research laboratory                                                                    | 13  |

|-------------------------------------------------------------------------------------------------------|-----|

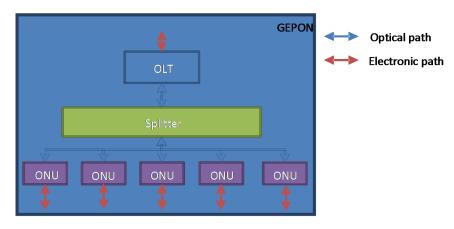

| Figure 2.2 GEPON system                                                                               | 14  |

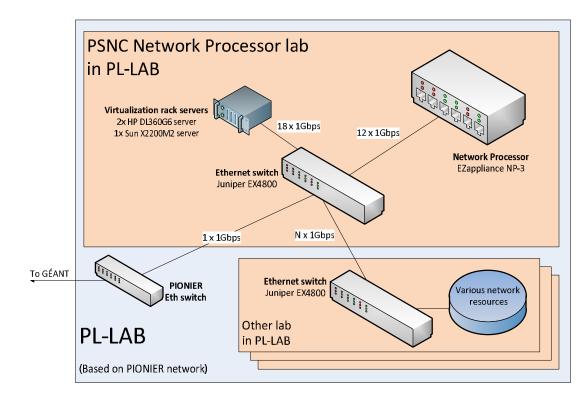

| Figure 2.3 PSNC network processor laboratory                                                          | 15  |

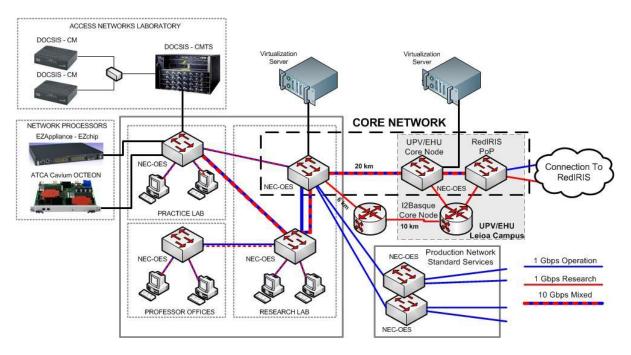

| Figure 2.4 UPV/EHU OpenFlow Enabled Facility                                                          | 16  |

| Figure 2.5 EICT's test environment                                                                    | 17  |

| Figure 2.6 EICT testbed topology                                                                      | 18  |

| Figure 2.7 University of Bristol testbed                                                              | 19  |

| Figure 2.8 DELL/Force10 testbed                                                                       | 21  |

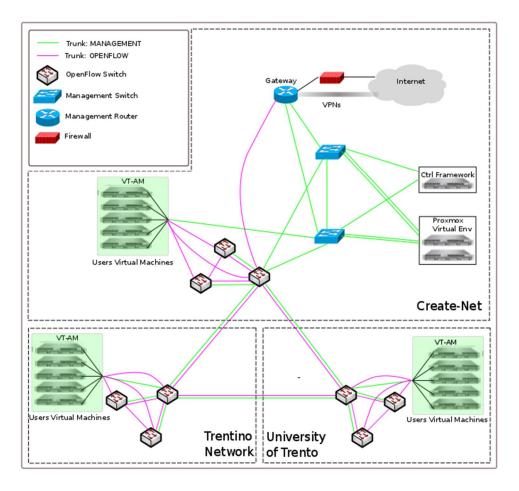

| Figure 2.9 CREATE-NET island topology                                                                 | 22  |

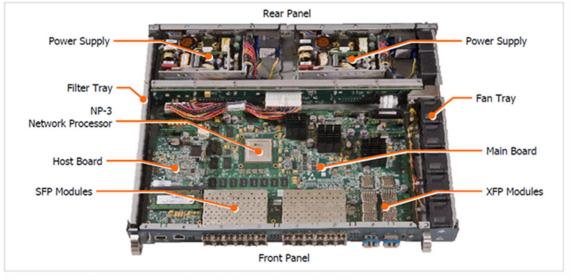

| Figure 3.1 EZappliance network device from EZchip Technologies                                        | 24  |

| Figure 3.2 EZappliance - Internal system layout [EZapp]                                               | 25  |

| Figure 3.3 EZappliance – logical architecture [EZapp]                                                 |     |

| Figure 4.1 The EPL-1000 OLT                                                                           | 31  |

| Figure 4.2 EPN 102 ONU                                                                                | 31  |

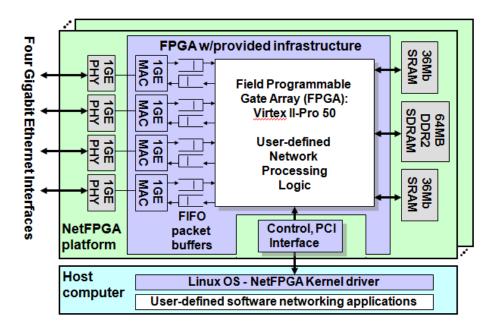

| Figure 5.1 The NetFPGA card                                                                           | 35  |

| Figure 5.2 Logical structure of the NetFPGA card                                                      |     |

| Figure 5.3 Two possible approaches to design project for NetFPGA card                                 | 38  |

| Figure 5.4 Diagram of the reference pipeline [netfpgareferenceNIC]                                    |     |

| Figure 5.5 The reference user data path [netfpga-buffer]                                              | 39  |

| Figure 5.6 Packet format inside the NetFPGA card                                                      |     |

| Figure 6.1 The Cisco uBR7246VXR Universal Broadband Router at the EHU-OEF                             | 43  |

| Figure 6.2 The Cisco uBR7246VXR chassis                                                               | 43  |

| Figure 6.3 The Cisco uBR7200-NPE-GI                                                                   | 44  |

| Figure 6.4 The Cisco uBR-MC16U                                                                        | 44  |

| Figure 6.5 The Cisco Modem/EPC3825                                                                    |     |

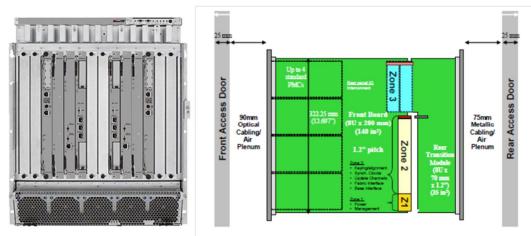

| Figure 7.1 Left: typical (here: 14-slot) ATCA shelf; Right: mechanical specification of an ATCA blade | 50  |

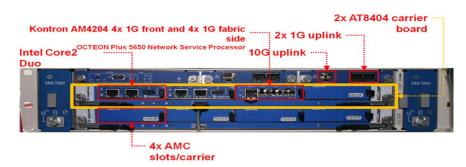

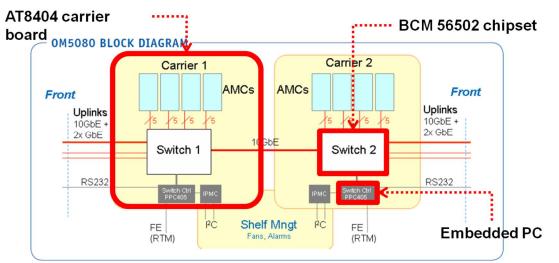

| Figure 7.2 KONTRON OM5080 shelf equipped with two AT 8404 carrier boards each capable of carrying 4   | AMC |

| cards                                                                                                 | 50  |

| Figure 7.3 Datapath layout of Kontron ATCA OM 5080 configuration, AMC cards can be equipped with Int  | tel |

| PCs or OCTEON Cavium Network Processors.                                                              | 51  |

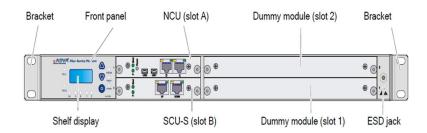

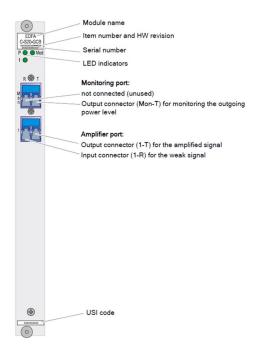

| Figure 8.1 SH1HU-R shelf                                                                              |     |

| Figure 8.2 SH7HU shelf                                                                                | 54  |

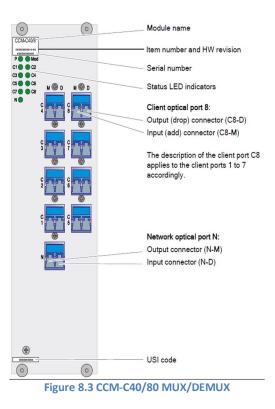

| Figure 8.3 CCM-C40/80 MUX/DEMUX                                                                       |     |

| Figure 8.4 EDFA-SGCB amplifier                                                                        |     |

| Figure 8.5 EDFA-DGCV amplifier                                                                        | 57  |

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

| D3.1 Hardware platforms and switching constraints | ALIEN |

|---------------------------------------------------|-------|

| Figure 8.6 8ROADM-C40                             | 58    |

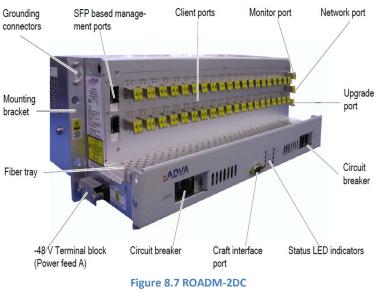

| Figure 8.7 ROADM-2DC                              |       |

| Figure 9.1 Switch external view (ports)           | 65    |

| Figure 9.2 Switch external view                   |       |

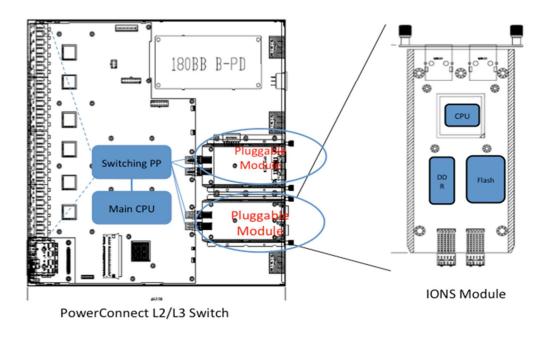

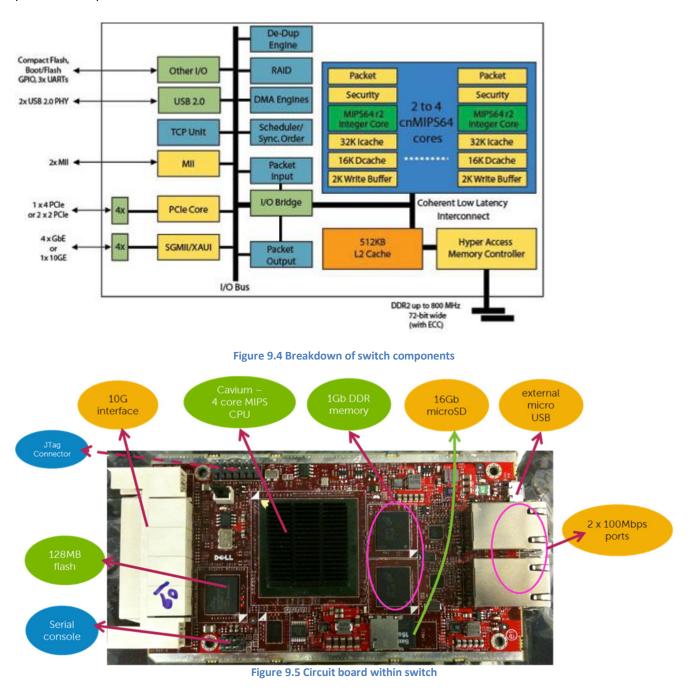

| Figure 9.3 Switch schematics                      | 66    |

| Figure 9.4 Breakdown of switch components         | 67    |

| Figure 9.5 Circuit board within switch            |       |

## **Table Summary**

| Table 3-1 Search structures in NP-3                                           | 27 |

|-------------------------------------------------------------------------------|----|

| Table 3-2 Most important NP-3 API functions available in EZdriver API library | 28 |

| Table 10-1 Assignment of equipment to device types                            | 70 |

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## **Executive Summary**

This deliverable describes a wide range of equipment available in the ALIEN consortium in local test-beds. All this hardware is not yet OpenFlow capable. The goal of ALIEN is to allow the use of hardware capabilities through a unified access interface for control and management. The project will introduce a new layer, the Hardware Adaptation Layer (HAL), which is intended to hide the complexity of underlying hardware and provide an abstraction for OpenFlow agents.

The following equipment is considered in ALIEN and will be referred to as "alien hardware":

- NetFPGA cards,

- EZappliance based on EZChip NP-3 network processor,

- Cavium OCTEON Plus AMC network processor module in an ATCA system,

- Optical switches,

- EPON OLT and ONU units,

- DOCSIS hardware.

This report is considered as a database and source of information for features and capabilities of particular hardware components available in the project. The report provides all relevant information about each piece of equipment, including a physical box overview, specific data plane details (e.g. transmission technology or switching management) and control/management plane analysis (e.g. protocols exposed by equipment or configuration requirements). This document also reports some work already done in other research projects. Specifically, the document describes experiences with introducing OpenFlow on ADVA, optical ROADM equipment, performed by University of Bristol as a part of its contribution to OFELIA. This work is considered as a starting point for ALIEN and the HAL specifically in the optical domain.

The description of the alien hardware available in the consortium is preceded by an overall description of the partners' local test-beds. This information will be used in other project work packages while planning scenarios for an integration with OFELIA facilities and scheduling specific experiments (e.g. CCN application on an OpenFlow environment).

The document introduces the concept of common hardware themes. This is the first attempt to create thematic groupings of alien hardware which can be treated in in a similar way by while designing the HAL.

## 1 Introduction

This document contains descriptions of the partner testbeds and, more importantly the target hardware for ALIEN. A major outcome for the ALIEN project is to implement OpenFlow on new hardware platforms via a common "Hardware Abstraction Layer" or HAL. This hardware will be described throughout this document as ALIEN hardware. The document provides the descriptions for each piece of hardware where OpenFlow will be implemented in such detail as to aid the design of the HAL. For this reason the document contains precise details of the hardware in terms of data and control plane both in terms of capabilities and in terms of protocols used.

The structure of the document is as follows: in section 2 the testbed at each partner site is described at a high level. This is to provide context for the later description of the ALIEN hardware. In sections 3 through to 9 the specific pieces of hardware are described in detail. Section 10 brings together common threads from the equipment description to create the building blocks for the HAL. Section 11 provides conclusions for this deliverable and, in particular, brings out those points most important for HAL design which can be learned from detailed analysis of the hardware.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 2 Testbeds

This section describes briefly the testbed available at each ALIEN partner site. The specific description of the ALIEN hardware available is deferred to a subsequent section.

## 2.1 **PUT testbed**

The PUT testbed consists of multiple network hardware entities delivering functionalities of all layers of ISO/OSI network model. The equipment is as follows:

Router Juniper MX240 3D Universal Edge Router – an Ethernet-optimized edge router that provides both switching and carrier-class Ethernet routing, with a capacity of up to 240 gigabits per second (Gbps), full duplex. The MX240 router enables a wide range of business and residential applications and services, including high-speed transport and VPN services, next-generation broadband multiply services, and high-volume Internet data center internetworking. All ports on this equipment have a speed of 1Gbps.

Alcatel-Lucent SR 1 7750 Service Routers – two powerful routers of service provider class. Both are equipped with 10 SFP Ethernet ports with the speed of 1Gbps each.

- About 20 Cisco Enterprise router and L2/L3 switches (mostly series C2800, C3560) this equipment is used as a referenced or access network, it is also used with CCNA/CCNP Cisco Networking Academy.

- 3 high performance virtualization servers from HP each of them has two multicore processors (Xeon),

24 GB RAM, 2 TB HDD space, 6 Ethernet ports with the speed of 1Gbps each. It makes these servers a powerful tool for any experiments with a lot of virtual machines on it.

- The Network processor NP3 EZappliance two applications of NP3 network processor from EZchip. Each device has 24 Ethernet ports with the speed of 1 Gbps. This device can be programmed with dedicated environment and language. It can process Ethernet frames in almost any way.

- Demo VoIP network PUT's educational and research laboratory network contains 3 dedicated VoIP protocol servers, 15 hardware and a lot of software IP phones. It is connected to the Internet and cooperate with the real VoIP operator.

- The Spirent Network Test Center it is a powerful network analyzer with a very wide range of possible tests and protocols. It can generate artificial network traffic and allows measurement of many parameters, including delays with using a GPS clock. This model contains 4 Ethernet ports with the speed of 1 Gbps.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

Optical Switch 4 x 1 x 2 for fiber with 1550 nm.

All of this equipment is connected into one network with two Juniper EX 3200 switches (see Figure 2.1). They offer almost 100 ports with the speed of 1 Gbps. We also use smaller switches from Cisco and Dell. In addition we can use a lot of PCs as a workstations or clients for this network.

The PUT testbed has a direct connection to the Polish Optical Internet (PIONIER) which is also a gateway to pan-European GEANT network. Therefore, PUT testbed can be reached by a research community from all Europe and even from around the world.

An important part of the PUT input is a laboratory of NetFPGA cards. It consists of 12 NetFPGA cards, that allow the testing of any new protocol within the hardware structures of FPGA Chip. These cards are programmable in VHDL or Verilog code. They realize programmed operations directly in the hardware structure of the main chip. Each such card consists of 4 Ethernet ports with a speed of 1 Gbps. They are hosted by high performance PCs which can stand for experimental network nodes. In addition to that an FPGA laboratory is deployed with FPGA cards based on 5 demo boards with Virtex 5 chips from XIlinx. All these cards are equipped with at least 2 SFP Ethernet ports with the speed of 1 Gbps and many additional elements as VGA/DVI drivers, different memories, interfaces as SATA, and so on. We use also a lot of Spartans – smaller FPGA chips from Xilinx. More description of the NetFPGA cards can be found in section 5.

Figure 2.1 PUT research laboratory

PUT is planning to extend this environment with next generation NetFPGA cards with 4x10 Gbps Ethernet interfaces, and servers where these cards will be installed.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 2.2 UCL testbed

The centre of the UCL testbed is the Gigabit Ethernet Passive Optical Network (GEPON) which is described in section 3. The UCL Converged Networks Laboratory (CONNET) was built to enable collaborative and cross-layer research. It consists of an IP testbed running over core and access optical (EPON) equipment and providing a joint platform for cross-layer interoperability and convergence studies. The PON access network testbed contains all the necessary equipment to implement, test and integrate innovative ideas in PON media distribution. Equipment includes lengths of fibre from 100m to 100km, 2 x 1Gigabit Ethernet OLTs, a 16 way splitter, a split emulator, 20 ONUs, 3 1Gigabit NetFPGAs, 2 10 Gigabit NetFPGAs, a 24 port Cisco router with 10GE capability and a range of optical and electronic measurement equipment. The CONNET laboratory can be directly connected to the OFELIA's UNIVBRIS island through the Aurora link. Aurora is a dark-fibre network to support research on photonics and optical systems. It interconnects with research groups at five universities, and provides access to intermediate locations along each fibre path where additional equipment can be sited.

Figure 2.2 shows the GEPON which is the heart of the UCL testbed. The GEPON is described more fully in section 3. Ethernet input at the Optical Line terminal (OLT) is converted to an optical signal in a proprietary format. This is fed through a splitter which multiplexes the optical signal to all of the Optical Network Units (ONUs) which receive identical copies of the optical domain signal. Each ONU uses time dimension multiplexing to select which part of the signal is destined for that particular ONU. The signal is then converted back into the electronic domain by the ONU. In the UCL testbed the connections between the splitter and OLT and between the OLT and each ONU can be replaced by various lengths of optical fibre from a metre up to a kilometre. The ONU themselves can be terminated by various pieces of test equipment. The most likely experimental set up for the ALIEN project will be to use NetFPGA cards to provide test loads for the GEPON.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 2.3 **PSNC testbed**

The PSNC network processor laboratory is designed for performing tests with network processors devices which could be fully programmed to perform various network roles. It contains one EZappliance device based on NP-3 network processor, three HP servers and 1GbE Ethernet Juniper switch implementing tagged connections. Currently there are 12 ports of EZappliance and 18 ports of servers connected to the Ethernet switch which allows changes to the network topology and traffic passed by EZappliance depending the tests or demonstrations to be performed. PSNC rack servers are powerful machines (e.g.: 2x6 core processor with hyper-trading, 24GB RAM, 2TB disk space, 6x 1GbE ports) for deploying virtual machines with any required software like network control plane or management plane components, network applications, software traffic generators, etc.

The PSNC network processor laboratory is a part of PL-LAB infrastructure. PL-LAB is a Polish nationwide network testbed designed to facilitate research in the area of Future Internet carried out within the Future Internet projects [PL-LAB]. It allows researchers to create virtual laboratories, with guaranteed resources and direct physical access to laboratory equipment. Depending on requirements, PSNC may reserve more network processor (e.g.: up to eight EZappliance boxes) devices using PL-LAB for a period of time which will allow to perform more complex test scenarios and demonstrations.

The PSNC network processor laboratory can be connected to pan-European GÉANT network using PIONIER network hub in Poznan (PIONIER is a Polish NREN network operated by PSNC).

Figure 2.3 PSNC network processor laboratory

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 2.4 UPV/EHU testbed

The core of the UPV/EHU testbed is the EHU OpenFlow Enabled Facility (EHU-OEF). The EHU-OEF provides the researchers of the UPV/EHU with a shared infrastructure to test and validate their proposals in the area of networking. Several different experiments can be run simultaneously.

The OpenFlow enabled devices available at the EHU-OEF are seven NEC switches IP8800/S3640 OpenFlow enabled, two NetFPGA 1G cards and four OpenFlow-ready Wireless LAN Access Points (Pantou firmware). There are also two powerful machines devoted to deploying virtual machines (e.g. Sun Fire X4450 4xQuad-Core Intel Xeon, 64GB RAM, 1TB disk space, 4x 1GbE ports). Additionally, there is also measurement and analysis equipment with line-rate support for 1 Gbps, such as two Spirent Smartbit network analysers with GPS synchronization and a DAG capture board.

Regarding network processors devices, the UPV/EHU has recently acquired an EZappliance with a NP-3 network processor from EZchip and is currently involved in the purchase process of an ATCA-F140 40G AdvancedTCA Switch Blade with a Cavium Blade with two OCTEON CN5860 network processors.

Finally, there is an operational DOCSIS platform deployed in the access networks laboratory of the UPV/EHU. This equipment is connected to the EHU-OEF. The DOCSIS equipment is fully described in section 6. In brief, there are two different elements, the CMTS (1x Cisco uBR7246VXR Universal Broadband Router) and the cablemodem (12x Cisco Modem/EPC3825 GW EU-DOCSIS 3.0 802.11n).

The EHU-OEF is directly connected at 10 Gbps to the Spanish NREN (RedIRIS) and the Basque NREN (i2basque). The direct connection with RedIRIS gives the possibility to connect this infrastructure with i2CAT's OFELIA Island at layer 2, thus enabling the connection of the EHU-OEF to OFELIA.

Figure 2.4 UPV/EHU OpenFlow Enabled Facility

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 2.5 EICT testbed

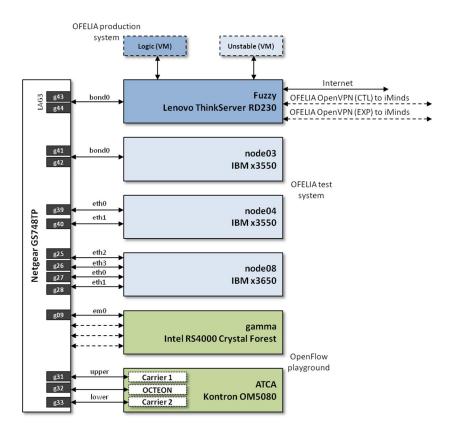

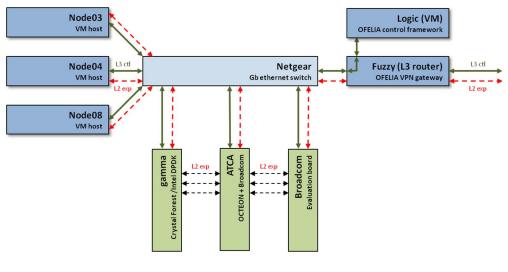

EICT's OpenFlow testbed serves two main purposes: (a) for testing upcoming releases of OFELIA's control framework, and (b) as a laboratory for hosting network hardware in the context of SDN/OpenFlow. Currently, the core is formed by a Kontron OM5080 ATCA compliant device and an Intel RS4000 server based on Intel's Crystal Forest platform. Based on the expedient framework initially developed at Stanford University, the OFELIA development team has significantly extended and improved the software resulting in the OFELIA control framework. All new major releases are tested within the EICT Island before entering production operation in other OFELIA islands.

Figure 2.5 EICT's test environment

The current network consists of two evaluation boards of Broadcom, 48 port GbE switches with 4 HighGig uplink ports, several IBM x3650 servers for hosting virtual machines, and the ATCA platform described in section 7.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

Figure 2.6 EICT testbed topology

## 2.6 Bristol testbed

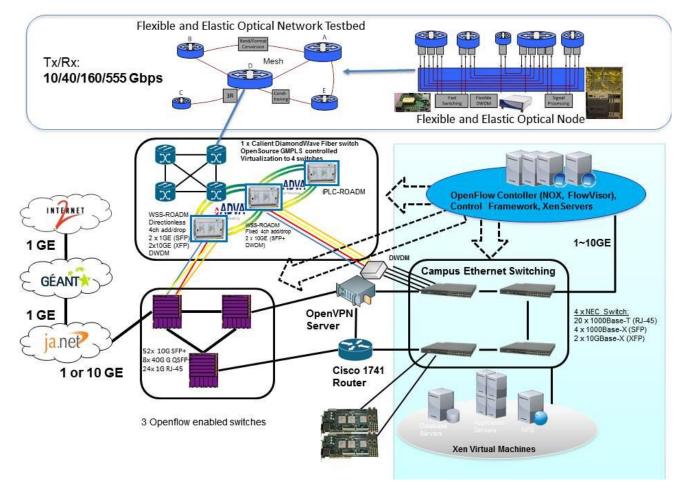

University of Bristol has experimental facilities that cover several layers and technological domains of optical and high performance networking allowing for advanced experimentation on network infrastructure/services/ applications. The lab features diverse transmission capabilities up to 500 Gbit/s, full photonic elastic (space/frequency/time) switching, high-performance software/hardware FPGA network platforms, Carrier Grade Ethernet testbeds, IP routers, and extended OpenFlow switches. Analogously, feature-rich proprietary and standardized yet control/virtualization/management systems are developed to deliver network-wide intelligence. These include multitechnology enabled SDN (OpenFlow-based, FlowVisor) as well as GMPLS/PCE systems. Such systems incorporate protocols and algorithms to deliver optical infrastructure control and virtualization.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

#### Figure 2.7 University of Bristol testbed

Architecture on demand and Multi-Dimensional Grid-less test-bed

- Architecture on-demand switching node

- Flexible Frequency/time/space transmission/switching

- High-speed Multi bit rate, multi format test-bed

- 160 GBPS OTDM, 74x10 GBPS, 15x40 GBPS RZ, NRZ

- Elastic bit rate, multi-format, and 555GBPS DMT, OFDM

Fixed/Flex Grid optical switching test-bed

- Four LambdaOpticalSystems LambdaNode2000 WDM switches

- o All optical wavelength/waveband switching

- GE ports, Alien Lambda ports, SDH 1G & 10G Ports

- Three ADVA FSP-3000 ROADMs (GMPLS controlled, OpenFlow enabled)

- GMPLS controlled Calient FibreConnect DiamondWave switch

- 2x Spectrum Selective Switches (C Band, C+L Band), OpenFlow enabled

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

L2 OpenFlow enabled Carrier Grade and campus network

- 3x Carrier Grade Ethernet OpenFlow switches (ARISTA 7050S 64, Brocade CES 2000 & One Extreme Summit X650 supporting 1/10/40 G interfaces)

- 4x NEC IP8800 switch,

- L3 IP test-bed

- Juniper router emulator (software router), 6 TB storage for media content

Software/Hardware Defined Network

- 5x high-performance servers with 10GE interfaces for Virtualization and OpenFlow-based control framework

- OF controllers

- NOX, FloodLight, SNAC

- Applications

- FlowVisor, Virtualization algorithms for multi-technology integration (packet-based, Fixed-Grid and Flex-Grid WDM)

- OpenVSwitch (soft switch)

- Software/Hardware-defined FPGA development platform/testbed

- o 3x Virtex 6-HXT, Virtex IV, 2x Virtex II-Pro

- Network-on-Chip supporting dual L2 Eth. Frame L1 TSON and hitless switch-over

- o Architecture on demand network on-chip and off-chip

The UNIVBRIS lab infrastructure is enhanced by the underlying network connectivity facilities that include: a dark fibre network connectivity; 1 and 10Gbps dedicated wavelength services over the JANET network; high speed dedicated connectivity over JANET, GEANT, GLIF and Internet2 to many research institutions into Europe, North/South America and Japan and Asia.

## 2.7 Dell/Force10 testbed

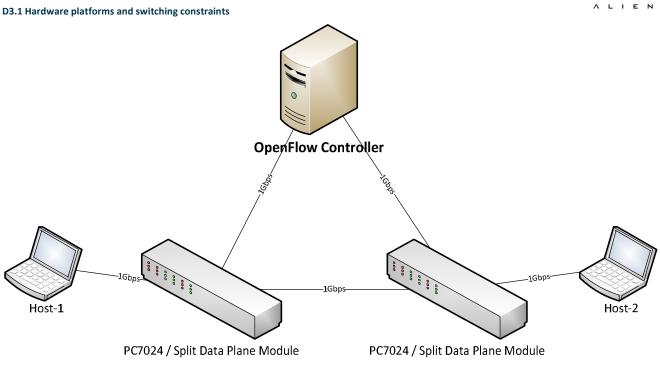

The Dell Force10 testbed will consist of two PowerConnect 7024 with a Split Data Plane module (SDPM) each. The Split Data Plane module will run a Linux Debian MIPS64. An external OpenFlow controller (FlowVisor / NOX or POX) running on the Dell Server PowerEdge to control the SPDM and or the PC7024 OpenFlow. Each SDPM has a serial console connection and external management Ethernet interface to allow full debugging and control.

The testbed is already configured to test different use case (encrypting flow, specific flow matching...) and the development environment is provided by the Cavium Software Development Kit.

Figure 2.8 DELL/Force10 testbed

## 2.8 CREATE-NET testbed

The CREATE-NET OpenFlow Testbed is based on a geographically distributed facility located in the city of Trento. The facility is composed of three different locations interconnected through a 10Gbps dedicated fiber pair (max. link distance 8.6 km) in a ring topology. The three locations of the experimental facility are: CREATE-NET, University of Trento (Department of CSEE) and Trentino Network , a public regional network operator which is providing Internet connectivity and other telecommunication services to the Public Administration all over the region.

Figure 2.8 shows the physical topology of the CREATE-NET testbed. The island has three NEC switches model IP8800/S3640-24T2XW interconnected via XFP optical transceivers in a 10Gbit ring. The other equipment (two HP Procurve 3500 and four NetFPGA cards) are interconnected using 1Gbit Ethernet interfaces. All the OF-enabled switches are OF 1.0 compliant. As depicted, the island is split into three sub-islands each of them located at different sites of the testbed and including three OpenFlow switches and one server hosting users VMs.

The management servers (OFELIA Control Framework, FlowVisor, NFS, SMB, Monitoring, Backup, ProxMox Virtual Environment) are hosted by the CREATE-NET server farm. Each OpenFlow switch acts as a hybrid switch: half of the ports are OpenFlow Controller, and half are directly managed by the standard protocols programmed in the firmware. The subislands are interconnected both via a dedicated fiber link (for the OpenFlow traffic) and using QinQ over an MPLS network for management purposes (to allow out-of-bound connection between the switches and the controller). Besides the OpenFlow network, the island provides also these networks that follow the OFELIA addressing convention:

- Control network (VLAN 4094 NET 10.216.32.0/22)

- Management network (VLAN 4093 NET 10.216.160.0/22)

Project:ALIEN (Grant Agr. No. 317880)Deliverable Number:D3.1Date of Issue:28/02/2013

• Internet network (VLAN 4092 – NET 172.16.0.0/24)

#### Figure 2.9 CREATE-NET island topology

Below the list of the entire inventory in the testbed, separated in OpenFlow hardware, non-OpenFlow (management) network equipment and Servers.

The Open Flow switches consist of:

- 3x NEC IP8800/S3640-24T2XW

- 2xHP ProCurve 3500

- 2xHost PC each with 2xNetFPGA cards (each NetFPGA has 4x1G ports)

The networking equipment includes:

- 3x Dell Switch power connect 5324

- 1x Dell Router (Vyatta Linux distro) working as a gateway, firewall, OSPF ABR and VPN endpoint The servers include:

- 3x servers running Debian Squeeze 32-bit

- 1x server running Vyatta Core 6.4

- 3x servers running Debian Squeeze 64-bit

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## **EZappliance**

## 3.1 **Overview**

The EZappliance network device is designed and produced by EZchip Technologies [EZchip], a company from Israel. It is a compact hardware platform for deploying network applications that provides a complete data plane and control plane solution. This device is designed for easy development and deployment of new efficient network applications. EZchip's NP-3 EZappliance platform is based on EZchip's NP-3 30-Gigabit network processor [EZapp]. This specialized network processor is a fully-programmable entity which enables flexible processing, parsing, classification, packet header manipulation, switching and management of pass through packets. The NP-3 integrated traffic manager (TM) provides wire-speed QoS functionality.

EZchip Technologies provides a broad library featuring tested source code for a wide range of applications, such as L2 switching, Q-in-Q, PBT, T-MPLS, VPLS, MPLS, IPv4/IPv6 routing, firewall and IDS. Such libraries enable implementation of different network applications like carrier Ethernet access and metro switches/routers, traffic management, security, gateways, network monitoring and traffic analysis [EZapp].

## 3.1.1 Physical box overview

EZappliance is 1U system which offers twenty-four 1-Gigabit Ethernet and two 10-Gigabit Ethernet ports (Figure 3.1).

Figure 3.1 EZappliance network device from EZchip Technologies

Beside the main board with an NP-3 network processor, this device is equipped with a HostCPU embedded system with a pre-installed ELDK Linux system. HostCPU is based on the PowerQUICK<sup>™</sup> III 800MHz general purpose processor with PowerPC architecture. The combination of the EZchip network processor and a general purpose CPU provides a complete data plane and control plane solution. NP-3 and Host CPU are interconnected by a PCI bus with throughput around 2Gbps. The NP-3 API routines and dedicated, pre-installed software on the HostCPU allow easy on-the-fly control of network processor actions. A data plane based on the NP-3 network processor with specialized Task Optimized Processors (TOPs) and a control plane based on HostCPU board with Linux OS are described in detail in sections 3.2 and 3.3 respectively.

The EZappliance device houses the following external interfaces:

- 24 x 1GbE SFP ports

- 2 x 10GbE XFP ports

- 10/100/1000 Ethernet and RS232 management ports

The HostCPU board is equipped with:

- Freescale PowerPC 800MHz CPU

- Linux ELDK 2.6.24-EZ.1

- 512MB RAM

- 64MB + 192MB flash memory

- PCI bus to NP-3 processor (up to 2Gbps)

- One 10/100/1000 Ethernet port

The internal system layout is depicted in Figure 3.2. Main modules like the main board with NP-3 processor and SFP and XFP modules, Host Board as well as Fan Tray, Filter Tray and two hot-swappable Power Supplies are shown.

SFP - Small Factor Pluggable XFP - 10 Gigabit Small Factor Pluggable Figure 3.2 EZappliance - Internal system layout [EZapp]

## 3.2 Data plane

### 3.2.1 Transmission technology

The data plane part of the EZappliance consists of the NP-3 network processor with associated memory and Ethernet MACs (Vitesse VSC7344) which means that the NP-3 is able to process Ethernet-based frames only. The data plane programmer is responsible for configuration and programming of all internal NP-3 entities to handle Ethernet frames together with all higher layers network headers and payloads.

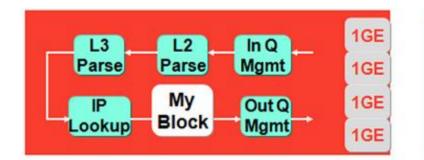

Key components of NP-3 processor are five pipelined Task Optimized Processors (TOPs) and Traffic Manager (TM) as depicted on Figure 3.3. Each TOP processor is specialized in performing specific operations over processed Ethernet frames. All TOPs except TOPsearch II are programmable in EZchip assembler with different instruction sets for each TOP. The data plane programmer must implement four separate programs for four programmable TOPs and load them into the NP-3 memory.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

D3.1 Hardware platforms and switching constraints **Host CPU** (Linux) **Control Plane** Eth0 EZdriver API PCI **EZchip NP-3** Eth 1 Data Plane Eth22 ТОІ TOF ТОР TOP Search Parse Resolve Modify Eth23 Eth24

Figure 3.3 EZappliance – logical architecture [EZapp]

**TOPparse** is designed for decoding, parsing and analysing received frames. It prepares searching keys for TOPsearch I and can pass message with some additional data to TOPresolve. The TOPparse instruction memory can contain up to 9000 instructions. This TOP has access to the entire processed frame.

**TOPsearch I** is designed for performing search operations on defined search structures (described in 3.2.2). Searching keys are prepared by the previous TOP, but there is also a possibility to perform compound searches in multiple structures with optional assembler code. This TOP can be programmed with up to 256 instructions and have no access to a processed frame data. It is primarily a search TOP.

**TOPresolve** has the main task of taking routing/forwarding decisions based on TOPsearch I results and messages from TOPparse. It can be programmed with up to 9000 instructions and have additional logical instructions. The outputs from this TOP are search keys for TOPsearch II and messages to TOPmodify. It has no access to processed frame data.

**TOPsearch II** is a second search TOP. It has limited possibilities in relation to TOPsearch I. It has no instruction memory so it is the only non-programmable TOP in NP-3 pipeline.

**TOPmodify** is designed for performing operations on a frame body according to TOPsearch II results and messages from TOPresolve. Each byte in a frame can be inserted, cut or overwritten. After processing a prepared frame is sent to the proper output queue in the Traffic Manager.

**Traffic Manager** is a configurable entity responsible for traffic shaping and scheduling that is located outside the TOPs. Its tree structure allows configuration of up to 64K "leaf" queues. Frames from each queue are sent by proper physical or virtual ports. Virtual ports gives the possibility of sending frames to the Host CPU via PCI or to reprocessing via internal loopback.

## 3.2.2 Switching management rules

The primary ways to configure the behaviour of the data plane implementation on NP-3 are search structures. A data plane programmer defines which search structures should exist within NP-3 and specifies the purpose and size of each search structure. The usage of search structures is coded within NP-3 assembler programs. Search structures can be accessed from TOPparse, TOPsearch I and TOPsearch II. Entries in all defined structures can be managed by Host CPU. EZappliance have totally 128Mbytes of search memory which can be divided between all defined search structures.

EZChip NP-3 network processor has some constrains in assigning search structures to TOPs. Up to 4 Direct Tables and Hash Tables can be accessed by TOPparse processor but search structures are used generally by TOPsearch processors. TOPsearch I can have access to 64 defined structures and TOPsearch II to 8 structures. Each search structure can be also aliased to the same TOP or another one. The usage of Ternary Content Addressable Memory (TCAM) allows for the addition of key masking in tree structures. In each entry in a tree structure bits of key field can be one, zero or "don't care". Detailed description of available search structures is presented in Table 3-1.

| Structure type                                         | Key size [B] | Result size [B]         | Structure type       | Key size [B] | Result size [B] |

|--------------------------------------------------------|--------------|-------------------------|----------------------|--------------|-----------------|

| TOPsearch I structures                                 |              | TOPsearch II structures |                      |              |                 |

| Direct Access Tables                                   | 1-4          | 8, 16, 32, 64           | Direct Access Tables | 1-4          | 8, 16, 32       |

| Hash Tables                                            | 1-48         | 8, 16, 32, 64           | Hash Tables          | 1-32         | 8, 16, 32       |

| Trees         1-16, 38         1, 3, 8, 16, 32, 64, 96 |              | TOPparse structures     |                      |              |                 |

| Linked: Hash + Tree                                    | 1-38         | 8, 16, 32, 64, 96       | Direct Access Tables | 1-3          | 8, 16, 32       |

| Linked: Tree + Hash                                    | 4            | 8, 16, 32, 64           | Hash Tables          | 4, 8, 12     | 8, 16, 24, 28   |

Table 3-1 Search structures in NP-3

Thanks to freedom in the implementing frame processing mechanisms and defining all supporting data structures, in the NP-3 there can be implemented a very broad set of switching rules. Incoming Ethernet frames can be switched to any EZappliance data plane port or sent to HostCPU depending on any combinations of protocol headers fields values or offset bytes values in a processed frame. The NP-3 processor allows also for looping and multiple passing of the same frame through TOPs pipeline which give even more possibilities.

## 3.3 Control/management plane

## 3.3.1 Plane purpose

The control/management plane does not exist in an EZappliance device unless it is installed by a device programmer. The EZappliance device is designed in such way that control plane or management plane software should be installed within a HostCPU Linux system. In a host system, there is pre-installed by default special software for accessing the forwarding plane named EZdriver API library, which must be used by any developed software which will interact with the data plane part of the device (NP-3 processor). The EZdriver API library allows installation of assembler programs for each TOP processor, management of TOP programs execution environment and TM modules configuration.

A more detailed description of EZdriver API library is presented in Table 3-2.

| EZdriver API functionality | Managed element of NP-3                  | Description                                                                                                                                                                                                                    |

|----------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data structures access     | TopParse<br>TopSearch                    | Operates on data structures initialized within NP-3 network processor. There is offered full access to read entries from structures, add new entries, modify existing entries or delete entries.                               |

| Memory/registers access    | CREG                                     | Allows to read from and write a new values to registers of NP-3 processor.                                                                                                                                                     |

| TM configuration           | WFQ<br>Shaping<br>WRED<br>Queue priority | Allows for configuration of Traffic Manager<br>components. Various traffic management<br>mechanism could be configured with proper<br>parameterization.                                                                        |

| Statistics access          | Counters                                 | Operates on building counters. State of counter can be set, reset and read.                                                                                                                                                    |

| Frame access               | Frame memory                             | Allows for passing frames between NP-3 and<br>HostCPU system. Frame generated with Host<br>system can be sent via data plane port as well as<br>frame received at data plane input port can be<br>forwarded to HostCPU system. |

Table 3-2 Most important NP-3 API functions available in EZdriver API library

Most fundamental NP-3 API functions are memory data structure operations within TopParse and TopSearch processors and operations within CREG and CAM registers. These data structures are used for the creation of routing or switching tables and storing some configuration values. Frame access functionality provided by EZdriver API library is very important for control plane components installed within Host system because allows to exchange control plane messages via data plane connections. A management agent installed within the host system can utilize statistics and counter access for any monitoring requirements. Both control plane and management plane systems can use TM configuration to implement different traffic conditioning and QoS mechanisms within the device.

The EZdriver API is provided in form of C headers files which must be included in any developed C program. In order to use the EZdriver API functionality, an EZdriver API object must be instantiated within application and this object will provide access to the NP-3 chip functionality. Instantiation of the EZdriver API object is quite complex. The workflow

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

includes initialization of the NP-3 host environment, memory partition, loading the prepared code and running it with a valid configuration for the NP-3 chip.

### 3.3.2 Exposed protocols

By default EZappliance device doesn't have any protocols installed within the host system. The host system allows for installation of additionally developed software which can handle any communication, signalization or routing protocols required by the role performed by the device.

### 3.3.3 Configuration requirements

An IP address of eth0 interface within the host system must be configured in order to allow installation of forwarding and control plane software. This IP address can be used as an end-point of the signaling control network (SCN) or the management network which allows cooperation between various control/management plane modules.

Additional configuration requirements depends on the role performed when a concrete frame forwarding and control plane software is installed within EZappliance.

## 4 **GEPON**

## 4.1 **Overview**

The GEPON at UCL consists of several components as shown in Figure 2.2. The whole GEPON system consists of the OLT, a passive optical splitter and several ONU. The OLT is the "intelligent" part of the system and in the normal deployment is the part which is connected to the WAN. It is a point-to-multipoint device and in normal deployment is connected to a splitter which multiplexes the signal to the ONU which are typically situated in end user premises. The exact product numbers are as follows:

- OLT: Planet technologies EPL-1000 <u>http://www.planet.com.tw/en/product/product.php?id=25817</u>

- Splitter: Planet technologies EPL-SPT-32

- ONU: Planet technologies EPN-102 <u>http://www.planet.com.tw/en/product/product.php?id=22826</u>

The OLT can sustain 1.25Gbps both upstream and downstream as can the ONU.

### 4.1.1 Physical box overview

The OLT has dimensions 432 x 207 x 43mm, taking up 1U of rackspace. It houses the following ports:

- Uplink: 1 x Gigabit TP / SFP Combo Port (10/100/1000Base-T / SFP GbE )

- PON Port: 1 x PON Port (IEEE 802.3ah)

- Console Port: RS-232 Serial Port (9600, 8, N, 1)

- Management Port: 1 x RJ-45 (10/100Base-TX)

The main processor controlling the OLT is the Teknovus TK3721 ASIC System-on-chip MAC controller.

Figure 4.1 The EPL-1000 OLT

The ONU has dimensions 176 x 124 x 35 mm (it is end user equipment not designed for rack mounting). It houses the following ports:

- LAN: 1 x 10/100Base-TX, Auto-Negotiation, Auto MDI/MDI-X

- LAN: 1 x 10/100/1000Base-TX, Auto-Negotiation, Auto MDI/MDI-X

- WAN: 1 (1.25G EPON interface with SC type connector, 1000Base-PX-20)

Figure 4.2 EPN 102 ONU

## 4.2 Data plane

## 4.2.1 Transmission technology

The data plane for the GEPON presents externally as a layer 2 Ethernet switch with 1GbE (10/100/1000Base-T / SFP GbE IEEE 802.3u) at the OLT and ONUs. Internally it is compliant with IEEE 802.3z (Ethernet over Fiber-Optic at 1 Gbit/s) and IEEE 802.3ah (Ethernet for the last mile) including Forward Error Correction support and an Operations Administration and Maintenance (OAM) protocol based on IEEE 802.3ah. It includes Dynamic Bandwidth Allocation (DBA) support and SLA systems. The system supports IPv4 and IPv6 packets and up to 4,000 MAC addresses. The GPON can allocate up to 4,096 VLANs.

Because of the passive nature of the splitter, this is an important bottleneck in the system. Transmission from the OLT to the ONU is one-to-many with an ONU selecting the data intended for it using time-domain multiplexing (TDM) techniques. This means that, while all ONU are capable of 1Gbps transmission this is not full mesh and, in fact, one ONU transmitting at 1Gbps whether to the external network (beyond the OLT) or to another ONU will completely fill the capacity of the GEPON. All transmission from ONU to ONU must be via the OLT (Because of the nature of the normal deployment of the system, transmission from ONU to ONU is not the usual mode and the majority of data will be between ONU and the external network.)

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

Transmission between the OLT, splitter and ONU is optical and entirely passive in nature. The system supports a split of up to 1:32 (that is 32 ONU) and is specified to use fibre lengths of up to 20km (which have been tested in our testbed). The system uses wavelength of 1310nm upstream and 1490nm downstream. The optical encoding uses IEEE 802.3ah (Ethernet in the first mile) and IEEE 802.3z (Ethernet over fibre optic) which implies conformance to 1000Base-PX10 or 1000Base-PX20. In particular, for point-to-multipoint applications IEEE 802.3ah introduces a family of signalling systems derived from 1000Base-X but with extensions to the Reconciliation (RS), Physical Coding (PCS), and Physical Medium Attachment (PMA) sublayers. In addition, IEEE 802.3ah includes FEC capability (Clause 60). In very general terms, upstream and downstream channels are wavelength duplexed, and traffic between ONUs and the OLT uses time division duplexing.

The OLT controls an ONU's transmission by the assigning of grants. The transmitting window of an ONU is indicated in GATE message where start time and length are specified. The point-to-multipoint (P2MP) transmission from OLT to ONUs mean that the equipment might not be seen as a switch but the entire GEPON regarded together can be thought of as a distributed switch. Access is controlled by Multi-Point MAC Control Protocol (MPCP). A point-to-point emulation sub layer assigns a Logical Link Identifier (LLID). The system supports multiple MAC addresses with several at the OLT (at least one for each ONU) and one at each ONU. The purpose of the MPCP is to allow point-to-point emulation using transmission that is naturally broadcast in nature (via the splitter). Multiple MACs operate on a shared medium by allowing only a single MAC to transmit upstream (from ONU to OLT) at any given time across the network using a time-division multiple access (TDMA) method. An LLID associates a MAC at an ONU to a MAC at the OLT and they are prepended to the data frame. In addition to such unicast LLIDs, broadcast LLIDs are used. New ONUs are automatically discovered and assigned a MAC at the ONU and OLT and an LLID binding them.

## 4.2.2 Switching management rules

The switching management for the GEPON is controlled by the OLT. Rules for filtering (dropping packets) can be created which match against MAC, VLAN or LLID identifiers. These rules can be AND rules only although several are allowed. Rules can also be created for classifying traffic according to similar identifiers. These rules can be used to place traffic into different priority queues or to different links. The configuration and filtering rules are set at the OLT but can be pushed out to the ONUs.

VLANs can be configured following the IEEE 802.1q protocol. The VLANs can connect the OLT to one or more ONUs and this allows the possibility of multicast at the GEPON.

The OLT can configure filtering and classification rules based upon MAC addresses or VLAN identifiers. These rules can The OLT can also be configured as a layer 3 bridge and, hence, learn IPv4 destination addresses.

## 4.3 Control/management plane

## 4.3.1 Plane purpose

The GEPON is primarily managed at the OLT and the management system is based upon the Teknovus TK3721 chipset developed by Teknovus but now owned by Broadcom. The OLT is responsible for creating and destroying logical links

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

between ONU, creating and maintaining SLAs (IEEE 802.1p), VLANs (802.1q) and other packet transmission rules. Traffic classification can involve layer 2, 3 and 4 rules. The operation of P2MP network is asymmetrical, with the OLT assuming the role of master, and the ONUs assuming the role of slaves.

The control plane can assign various algorithms to change the rate of the PON Traffic. The device uses a hierarchical weighted round robin algorithm for Dynamic Bandwidth Allocation. This allows, for example a shaper which restricts user traffic to enforce SLAs. Maximum and minimum bandwidths for an ONU to OLT connection can be specified. The DBA is implemented by changing the time slots granted to an LLID.

Port management can be used for several actions. Ports can be set to loop-back. VLANs can be allocated to single or multiple LLIDs (allowing multicast). ONUs can be cross connected to allow a logical connection directly between ONUs. A link from OLT to ONU can be set as a network bridge. Links can also be blocked, cutting an ONU off from the OLT. The OLT can use filtering rules to classify traffic. The OLT can also be configured as a layer 3 bridge.

## 4.3.2 Exposed protocols

The control channel between the OLT and the ONU is based on the standard IEEE 802.3ah Operation, Administration and Management (OAM) protocol (Clause 57). Architecturally, the OAM sublayer is an optional sublayer placed between the Media Access Control (MAC) and the Logical Link Control (LLC) sublayers within IEEE 802.3ah, and has the following objectives:

- 1. *Remote Failure Indication*. This allows the OLT to verify whether a particular ONU is operational.

- 2. *Remote Loopback*. This allows for traffic sent to the ONUs to be returned to the OLT for error testing.

- 3. *Link Monitoring*. This provides a channel for event notification that allows the inclusion of diagnostic information, as well as providing a mechanism for polling variables within the IEEE 203.3a MIB (Clause 30).

- 4. *Miscellaneous*. This allows the OLT to query the ONUs for capability discovery, as well as to allow proprietary higher layer management applications.

Control requests to the PON must be made via one of the two management ports of the OLT. A console port and a management port are available. The protocols are proprietary and specific to the TK3721 ASIC.

The console port is an RS-232 serial port and accepts text-style commands via a standard terminal application. A standard console terminal can send commands using a slash delimited command line interface. Commands must be sent "spaced out" to not overwhelm the send/receive rate of the serial port. Example commands are:

/pers/mgmtip <IP address> -- change the IP address of the management port.

/oam/dump <LLID> -- dump OAM statistics for the specified LLID.

The management port is an RJ-45 (10/100Base-TX). It accepts commands via a closed source proprietary GUI. This communicates the commands using UDP and a proprietary message format.

4.3.3 Configuration requirements

As previously stated, the GEPON can be configured via the console port (using the command line via a terminal window) or via a PC the management port using a GUI. The GUI is a windows based program and it must be run on a PC with an IP address matching that known for the management port by the OLT. This can be reset in the OLT using the serial port and a command of the form:

pers/hostip www.xxx.yyy.zzz

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

## 5 NetFPGA

## 5.1 The NetFPGA Card Overview

The NetFPGA card is an extension board for a PC (see Figure 5.1). It is connected with the PC via the PCI bus. It was designed and developed by researchers, students and engineers from Stanford University and the University of Cambridge. They created the NetFPGA groups and run the NetFPGA project [netfpga]. They prepared a lot of interesting examples and codes, most of them are available for free at website [netfpga].

Figure 5.1 The NetFPGA card

The NetFPGA can be treated as a low-cost hardware platform for running experimental networking devices. It was primarily designed as a tool for teaching networking hardware and router design. It has also proved to be a useful tool for networking researchers. Through partnerships and donations from sponsors of the project, the NetFPGA is widely available to students, teachers, researchers, and anyone else who is interested in experimenting with new ideas in high-speed networking hardware. It allows use of reference projects (IPv4router, Ethernet switch or Network Interface Card) or creation of its own prototypes and projects.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

A detailed description of the NetFPGA's operation is available in the official guide [netfpgaguide]. The NetFPGA codebase is open-source. Details about the license are described on-line. Researchers and students are free to use and modify the NetFPGA hardware and software code as they see fit. It is possible to directly use or modify prepared reference projects or prepare new ones.

### 5.1.1 Physical Box Overview

At a high level, the board contains four 1 Gigabit/second Ethernet (GigE) interfaces (they can be seen in Figure 5.1), a user programmable Field Programmable Gate Array (FPGA), and four banks of locally-attached Static and Dynamic Random Access Memory (SRAM and DRAM). It has a standard PCI interface allowing it to be connected to a desktop PC or a server. A reference design can be downloaded from the project website [netfpga] which contains a hardware-accelerated Network Interface Card (NIC) or an Internet Protocol Version 4 (IPv4) router that can be readily configured into the NetFPGA hardware. The router kit allows the NetFPGA to interoperate with other IPv4 routers.

The NetFPGA platform contains one large Xilinx Virtex2-Pro 50 FPGA. It is the main chip of this board. It should be programmed with user-defined logic, its core clock runs at 125MHz. The NetFPGA platform also contains next small Xilinx Spartan II FPGA holding the logic that implements the control logic for the PCI interface to the host processor.

The board contains also memory banks. They are realized by two 18 MBit external Cypress SRAMs, they are arranged in a configuration of 512k words by 36 bits (4.5 Mbytes total) and operate synchronously with the FPGA logic at the same frequency – 125 MHz. One bank of external Micron DDR2 SDRAM is arranged in a configuration of 16M words by 32 bits (64 MBytes total).

The Broadcom BCM5464SR Gigabit/second external physical-layer transceiver (PHY) sends/receives packets over/from standard category 5, 5e, or 6 twisted-pair cables. The four PHY interfaces with four Gigabit Ethernet Media Access Controllers (MACs) instantiated as a soft core on the FPGA. The NetFPGA also includes two interfaces with Serial ATA (SATA) connectors that enable multiple NetFPGA boards in a system to exchange traffic directly without use the PCI bus.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

### Figure 5.2 Logical structure of the NetFPGA card

The project designated to be run on the NetFPGA card contains two main parts – the software part and the hardware part. The software is typical software which interacts with the operating system of a PC. It also contains a typical driver for hardware. The hardware part of code is run in Xilinx Virtex II FPGA chip, which is the main chip of the card. It processes all the data from input queues and implements the program for the hardware part. Both parts cooperate via PCI bus with kernel driver and registers [netfpgaregisters].

The NetFPGA offloads processing from a host processor. The host's CPU has access to main memory and can DMA to read and write registers and memories on the NetFPGA. Unlike other open-source projects, the NetFPGA provides a hardware-accelerated hardware datapath. The NetFPGA provides a direct hardware interface connected to four GigE ports and multiple banks of local memory installed on the card.

NetFPGA packages (NFPs) are available that contain source code (both for hardware and software) that implement networking functions. Using the reference router as an example, there are three main ways that a developer can use the NFP. In the first usage model, the default router hardware can be configured into the FPGA and the software can be modified to implement a custom protocol.

Another way to modify the NetFPGA is to start with the reference router and extend the design with a custom user module. Finally, it is also possible to implement a completely new design where the user can place their own logic and data processing functions directly into the FPGA.

The hardware is used as an accelerator and then the software must be used to implement new protocols. In this scenario, the NetFPGA board is programmed with IPv4 hardware and the Linux host uses the Router Kit Software distributed in the NFP. The Router Kit daemon mirrors the routing table and ARP cache from software to the tables in the hardware allowing for IPv4 routing at line rate. The user can modify Linux to implement new protocols and test them using the full system.

Starting with the provided hardware from the official NFP (or from a third-party NFP), this can be modified using modules from the NFP's library or by writing your own Verilog code. The source code is then compiled using industry standard design tools to a bit file. The implemented bitfile can then be downloaded to the FPGA. The new functionality can be complemented by additional software or modifications to the existing software. For the IPv4 router, an example of this would be implementing a Trie longest prefix match (LPM) lookup instead of the currently implemented CAM LPM lookup for the hardware routing table. Another example would be to modify the router to implement NAT or a firewall.

# 5.2 Data Plane

# 5.2.1 Transmission technology

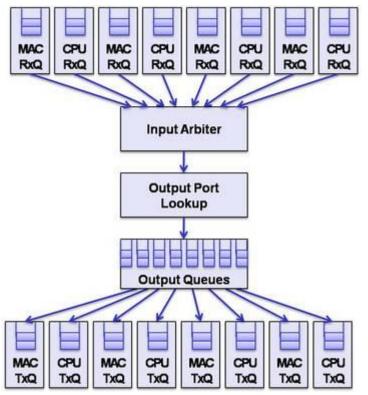

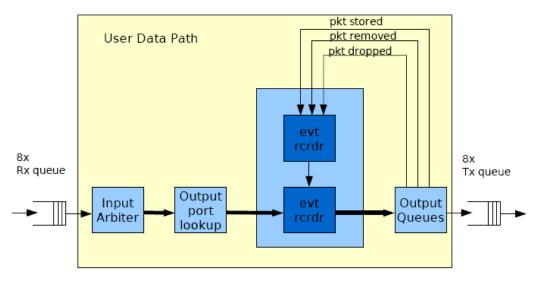

The main assumption was to implement the data plane in the hardware part, i.e. the data will be processed only by the hardware chip, which is the FPGA. It is possible to use clean state design, i.e. the user has to develop their own logic and data path for internal structure of FPGA chip. But it is much better to use a prepared reference pipeline and yourself develop only the additional functionality. Figure 5.3 shows the difference between two approaches.

| Project:            | ALIEN (Grant Agr. No. 317880) |

|---------------------|-------------------------------|

| Deliverable Number: | D3.1                          |

| Date of Issue:      | 28/02/2013                    |

1GE

1GE

1GE

1GE

#### D3.1 Hardware platforms and switching constraints

# **Customized Reference Router**

# **Clean-Slate Design**

My

Custom

Hardware

Figure 5.3 Two possible approaches to design project for NetFPGA card