The aim of Hardware Abstraction Layer (HAL) is to design and implement the required building blocks for a novel Hardware Abstraction Layer (HAL) that can facilitate unified integration of alien types of network hardware elements (i.e. network element that doesn’t support natively OpenFlow) with an OpenFlow control framework i.e. OFELIA control framework. The alien hardware are:

- traditional packet switching network elements (e.g., L2 switches),

- non-packet switching network elements (e.g., optical switch, NetFPGA),

- network monitoring and network processing elements (e.g. FPGA, Network processor).

This activity focuses on :

- Design and development of a suitable hardware description language that can facilitate uniform representation of any type of alien hardware and their capabilities

- Design and development of a hardware abstraction mechanism that together with the proposed hardware description language can interface with different type of alien hardware and can hide their complexity as well as technology and vendor specific features from OpenFlow control framework

- Redefinition of the classical OpenFlow data model to support new notions of flow, switching and processing in alien hardware

- Define the generic flow action i.e. switching, processing and monitoring to be performed on new flow concept

HAL architecture

Initial HAL architecture was described in the HAL whitepaper, publicly available document released by the ALIEN Consortium.

The Whitepaper describes the concept of Hardware Adaptation Layer (HAL) for applying the OpenFlow protocol to the non-OpenFlow hardware. The document describes motivation of designing the HAL and explains the high level goals. HAL whitepaper describes the HAL architecture and constitutes the guideline for the future steps in the ALIEN project – the implementation of the HAL on all available devices in the ALIEN project.

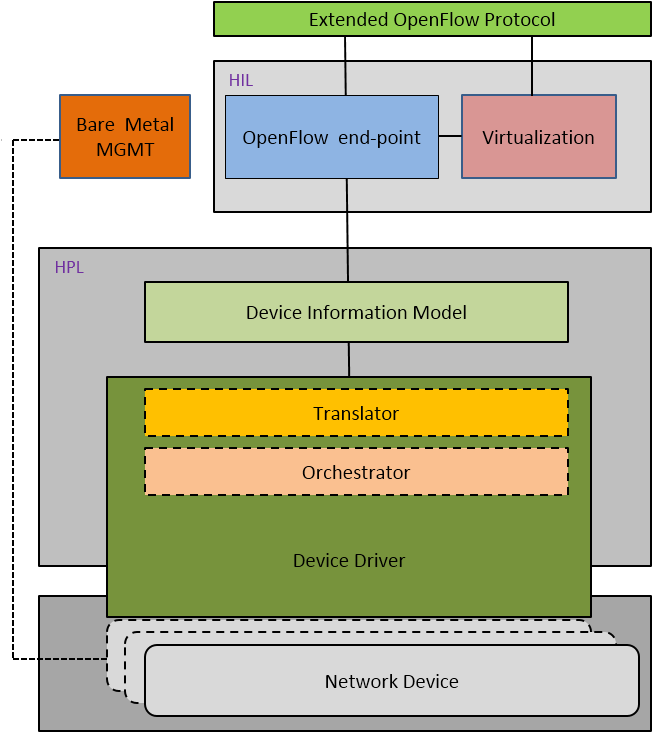

HAL unified architecture is divided into two:

- Hardware Agnostic Part (HIL – Hardware Interface Layer) – a set of components enabling virtualization and communication mechanisms that are independent of underlying hardware platform

- Hardware Specific Part (HPL – Hardware Presentation Layer) – a set of hardware drivers realizing atomic network instructions specific for all ALIEN platforms (i.e.: ATCA, DOCSIS, Dell/Force10 switch, EZappliance, GEPON, L0 switch, NetFPGA)

HAL implementation

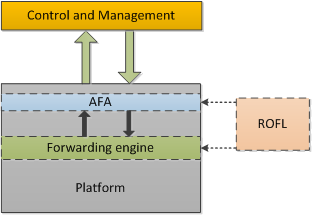

HAL implementation is based on ROFL and xDPd libraries. First source code for the HAL was released in May 2013.

The Revised OpenFlow Library (ROFL) helps you adding OpenFlow support to your software to build control applications, controller frameworks and/or data path elements.

The eXtensible DataPath daemon (xDPd) is a multi-platform, multi OF version, open-source datapath built focussing on performance and extensibility.